# AI310SM模组 产品手册

Date 2025-01-08

#### 北京品立科技有限责任公司保留一切权利。

非经本公司书面许可,任何单位和个人不得擅自摘抄、复制本文档内容的部分或全部,并不得以任何形式传播。

#### ★ 注意

您购买的产品、服务或特性等应受品立科技商业合同和条款的约束,本文档中描述的全部或部分产品、服务或特性 可能不在您的购买或使用范围之内。除非合同另有约定,本公司对本文档内容不做任何明示或暗示的声明或保证。

由于产品版本升级或其他原因,本文档内容会不定期进行更新。除非另有约定,本文档仅作为使用指导,本文档中 的所有陈述、信息和建议不构成任何明示或暗示的担保。

#### 了解更多产品 请扫码

公众号

视频号

#### 北京品立科技有限责任公司

网址: http://www.plink-ai.com/

地址:北京市海淀区上地三街金隅嘉华大厦C座1108室

联系电话: 400-127-3302

# AI310SM 产品手册修订记录

| 修订版   | 修订日期       | 修订内容                                                                                              | 适用硬件版本 |

|-------|------------|---------------------------------------------------------------------------------------------------|--------|

| V 1.0 | 2024-05-20 | 创建文档                                                                                              | V 1.0  |

| V 2.0 | 2024-09-26 | 更新CPU信息                                                                                           | V 1.0  |

| V2.1  | 2025-01-04 | 1、修改HCCS参考时钟描述:<br>模组内部已有100nF耦合电容<br>2、修改Board ID描述<br>3、SerDes时钟特征阻抗改为: 差分100±10%ohm; 数据特征阻抗改为: | V 1.0  |

#### 产品硬件修订历史

| 硬件版本  | 修订日期       | 修订内容          |

|-------|------------|---------------|

| V 1.0 | 2024-05-20 | 初始版本          |

| V 2.0 | 2024-09-12 | 修改部分IOPIN脚    |

| V 3.0 | 2025-02-12 | 修改部分IOPIN脚    |

| V 4.0 | 2025-10-14 | 修改EMMC大小为128G |

电子元件和电路对静电放电很敏感,虽然本公司在设计电路板卡产品时会对板卡上的主要接口做防静电保护设计,但很难对所有元件及电路做到防静电安全防护。因此在处理任何电路板组件时,建议遵守防静电安全保护措施。

#### 防静电安全保护措施包括但不限于以下几点:

- 1. 运输、存储过程中应将板卡放在防静电袋中,直至安装部署时再拿出板卡。

- 2. 在身体接触板卡之前应将身体内寄存的静电释放掉:佩戴放电接地腕带。

- 3. 仅在静电放电安全区域内操作电路板卡。

- 4. 避免在铺有地毯的区域搬移电路板。

- 5. 通过板边接触来避免直接接触板卡上的电子元件。

# 目录

| 1产品概述        | 5          |

|--------------|------------|

| 2 主要特性       | 6          |

| 3 技术规格       | 7          |

| 4 系统方案       | 8          |

| 5 原理框图       | ~          |

| 6 产品结构及布局    |            |

| 7 连接器定义      |            |

| 8接口说明        | 18         |

| 8.1 HCCS接口   | 18         |

| 8.2 SerDes接口 |            |

| 8.3 SPI接口    |            |

| 8.4 CAN接口    |            |

| 8.5 UART接口   |            |

| 8.6 I2C接口    |            |

| 8.7 USB接口    |            |

| 8.8 MDIO接口   |            |

| 8.9 LED信号    | ~ ·        |

| 8.10 GPIO    | <b>~</b> . |

| 8.11 双模组互联信号 | . •        |

| 8.12 配置信号    |            |

| 8.13 IPMC信号  |            |

| 8.14 其他信号    |            |

| 8.15 电源输入    |            |

|              |            |

# 1产品概述

AI310SM是一款基于昇腾310P芯片设计的高性能边缘推理模组,算力最高可达176 TOPS@INT8。CPU处理器为16core TaishanV200M,CPU主频1.9GHz,ARMv8.2架构;AI处理器为DaVinciV200,主频1.08GHz;板载48GB LPDDR4X内存;128G EMMC。

AI310SM模组采用高可靠性的工业级物料设计,任何变更均遵循JESD-046标准通过PCN通知。

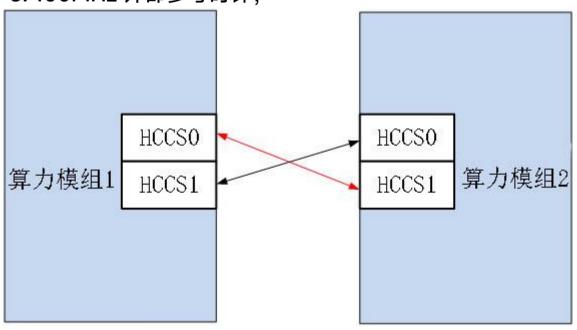

AI310SM模组支持通过HCCS总线进行芯片级双模组高速互联,互联总带宽可达 192Gbps。

# 2 主要特性

#### CPU

集成4个TaishanV200M MP4 cluster(16 core 64-bit)@max. 1.9Ghz,符合 ARMv8.2架构

- 支持DCLS、Split和Lock工作模式,可以通过cluster hard reset切换

- 支持SVE指令, NEON/FPU, Crypto, FP16 指令, vector inner product 指令

#### Al Core

集成10个DaVinciV200 AI core @max 1.08GHz

- 提供FP16 8TFLOPS per GHz, 或INT8/UINT8 16TOPS per GHz

#### Vector Core

集成8个DaVinciV200 Vector core @max 1.0GHZ

- 优化Point cloud segmentation、rasterization、OpticalFlowLK特征点提取和 跟踪等业务性能

- 支持training preprocess 图像增强处理

- 支持其他的常见Computer Vision算子(OpenVX 算子)

#### Video codec

支持12 channel 4K@60fps/96 channel FHD@30fps H.264/H.265 video decoder 支持3 channel 4K@60fps/24 channel FHD@30fps H.264/H.265 video encoder

#### Image codec

4K@384fps (FHD@2048fps) JPEG decoder 4K@192fps (FHD@1024fps) JPEG encoder

#### Image Pre-processing

支持up/down scaling, crop, Chroma up/down sampling, color space conversion(等效FHD 4320FPS)

# 3技术规格

| 序号 | 模块/类别  | 规格                                                            |

|----|--------|---------------------------------------------------------------|

| 1  | 处理器    | 昇腾310P                                                        |

| 2  | 显存     | 物理显存LPDDR4X 48GB                                              |

| 3  | EMMC   | 128GB                                                         |

| 4  | 调试接口   | 由FMC连接器引出一路UART调试串口                                           |

| 5  | PCIE接口 | 引出一路PCIE x16 接口,最高支持PCIE 4.0,向下兼容PCIE 3.0 /PCIE 2.0/ PCIE 1.0 |

| 6  | HCCS接口 | 8 lane HCCS信号,用于板间互联,最高速率支持<br>24Gbps/lane                    |

| 7  | 指示灯    | 一个电源指示灯、一个状态指示灯                                               |

| 8  | 电源     | 支持 12V 直流供电                                                   |

| 9  | 功耗     | ≤120W                                                         |

| 10 | 重量     | ≤0.5Kg                                                        |

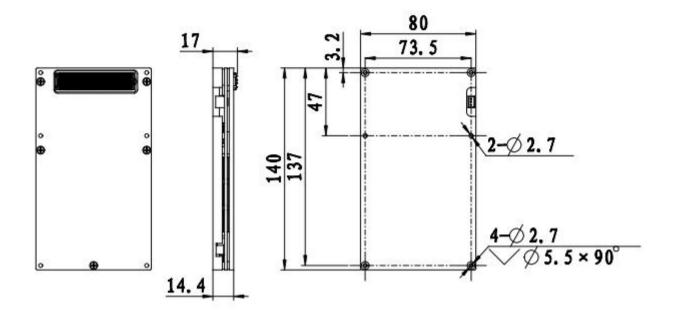

| 11 | 尺寸     | 板卡: 140mm*80mm<br>模组: 142.5mm*82.5mm                          |

| 12 | 环境适应性  | -40°C~+65°C(工业级)                                              |

| 13 | 操作系统   | 搭配银河麒麟驱动                                                      |

#### ・ 外部接口 External Interface

Serdes: 可复用为XGE, PCIe, SATA, HCCS接口

XGE: 最大支持8个XGE Serdes 接口, 速率支持 10.3125/5/2.5Gbps

PCIe: 最大支持1个PCIe Gen4 16X接口,兼容1X, 2X, 4X, 8X

SATA: 支持4个SATA3.0 接口,兼容SATA2.6,SATA2.0,SATA1.0

CAN-FD: 支持4路隔离CAN-FD接口

UART接口:支持4路三线制UART口,支持流控功能

I2C接口:支持4路I2C接口

SPI接口: 4路SPI接口

MDIO接口:支持2组MDIO接口 PWM接口:支持4路PMW接口 GPIO接口:支持8路可编程GPIO Al310SM datasheet 系统方案

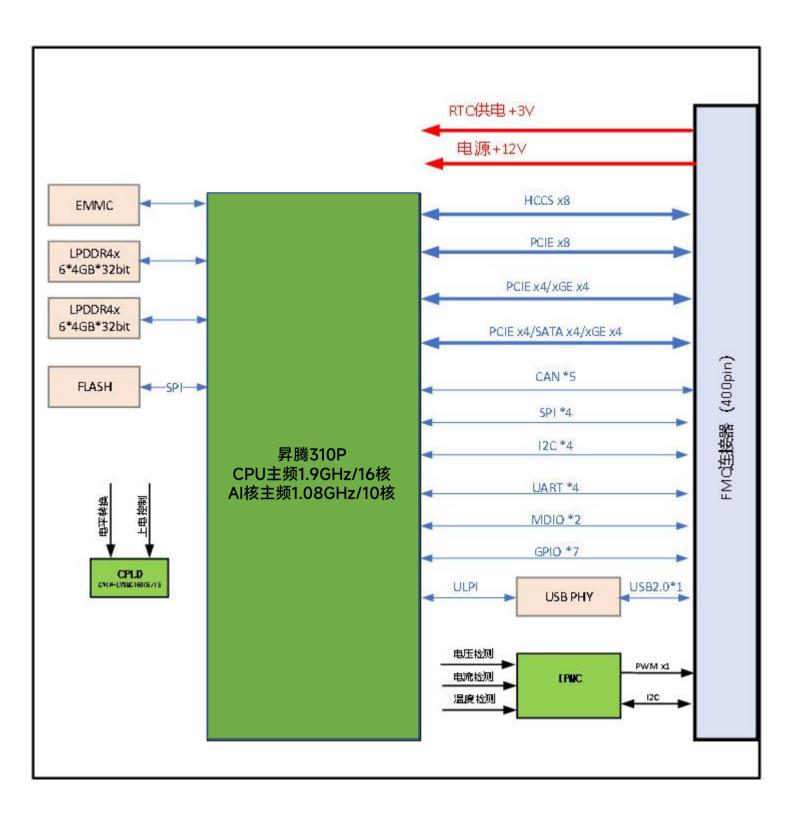

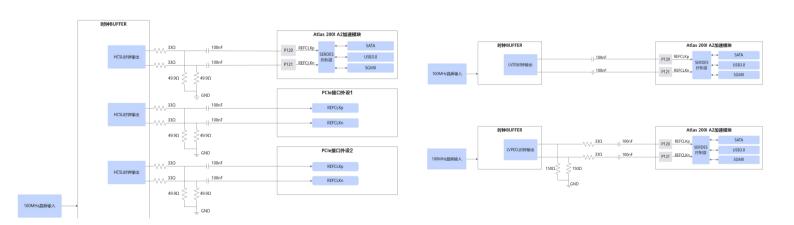

# 4 系统方案

下图为AI310SM算力模组的系统框图。因昇腾310P存在引脚复用情况,该系统框图仅展示默认出厂的引脚复用框图

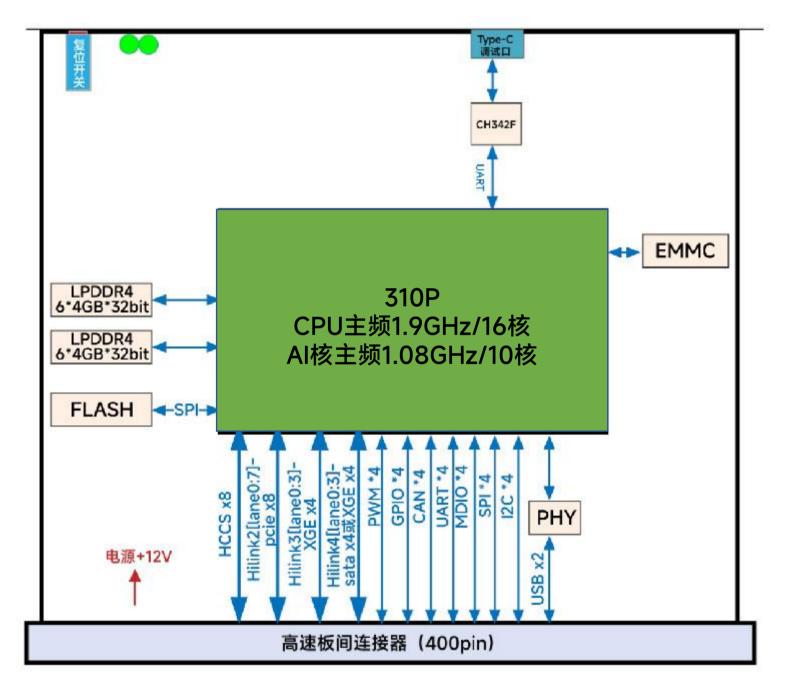

# 5 原理框图

#### AI310SM模组原理框图

| 订货型号      | 说明                                        |

|-----------|-------------------------------------------|

| Al310SM   | 基于昇腾310P设计的高性能边缘推理模组<br>工作温度: 0°C~+65°C   |

| Al310SM-I | 基于昇腾310P设计的高性能边缘推理模组<br>工作温度: -40°C~+85°C |

产品结构及布局

# 6 产品结构及布局

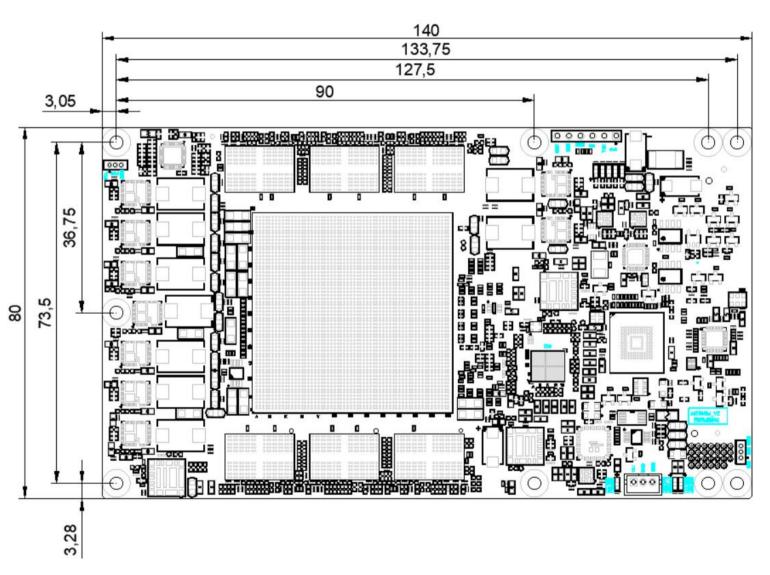

AI310SM算力模组板卡尺寸(PCBA): 140mm\*80mm(长×宽);

板卡(PCBA)尺寸示意图

产品结构及布局

## AI310SM PCBA实物图

连接器定义

# 7连接器定义

|            | FMC板对板设      | FMC板对板连接器                                                                                         |                                                 |                                                 |                                                 |                                                 |                                                 |                                                 |                                                 |      |

|------------|--------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|------|

| 模组插头<br>型号 |              | 鳌格诺电子有限公司:85EAM-40102010-109-C02,间距1.27mm,配接高度7mm<br>中航光电:FMC-40-02.0-S-10-2-A-T,间距1.27mm,配接高度7mm |                                                 |                                                 |                                                 |                                                 |                                                 |                                                 |                                                 |      |

| 载板插座<br>型号 | 鑫格诺电子有       | 限公司85EAF                                                                                          |                                                 | P-C02,间距1.27                                    |                                                 |                                                 |                                                 |                                                 |                                                 |      |

| Pin        | Α            | В                                                                                                 | С                                               | D                                               | Е                                               | F                                               | G                                               | Н                                               | I                                               | J    |

| 1          | P3V3_BA<br>T | P12V                                                                                              | P12V                                            | P12V                                            | P12V                                            | P12V                                            | P12V                                            | P12V                                            | P12V                                            | P12V |

| 2          | P12V         | P12V                                                                                              | P12V                                            | P12V                                            | P12V                                            | P12V                                            | P12V                                            | P12V                                            | P12V                                            | P12V |

| 3          | GND          | GND                                                                                               | GND                                             | GND                                             | GND                                             | GND                                             | GND                                             | GND                                             | GND                                             | GND  |

| 4          | GND          | GND                                                                                               | GND                                             | PCIE_100M<br>_CLKOUTn                           | PCIE_100M<br>_CLKOUTp                           | GND                                             | GND                                             | M_HCCS_R<br>EFCLKn                              | M_HCCS_R<br>EFCLKp                              | GND  |

| 5          | GND          | M_PCIE_T<br>X8p/XGE<br>0_TXp                                                                      | M_PCIE_TX<br>8n/XGE0_T<br>Xn                    | GND                                             | GND                                             | M_PCIE_RX<br>8n/XGE0_R<br>Xn                    | M_PCIE_RX<br>8p/XGE0_R<br>Xp                    | GND                                             | GND                                             | GND  |

| 6          | GND          | GND                                                                                               | GND                                             | M_PCIE_TX<br>9p/XGE1_T<br>Xp                    | M_PCIE_TX<br>9n/XGE1_T<br>Xn                    | GND                                             | GND                                             | M_PCIE_RX<br>9n/XGE1_R<br>Xn                    | M_PCIE_RX<br>9p/XGE1_R<br>Xp                    | GND  |

| 7          | GND          | M_PCIE_T<br>X10p/XG<br>E2_TXp                                                                     | M_PCIE_TX<br>10n/XGE2_<br>TXn                   | GND                                             | GND                                             | M_PCIE_RX<br>10n/XGE2_<br>RXn                   | M_PCIE_RX<br>10p/XGE2_<br>RXp                   | GND                                             | GND                                             | GND  |

| 8          | GND          | GND                                                                                               | GND                                             | M_PCIE_TX<br>11p/XGE3_<br>TXp                   | M_PCIE_TX<br>11n/XGE3_<br>TXn                   | GND                                             | GND                                             | M_PCIE_RX<br>11n/XGE3_<br>RXn                   | M_PCIE_RX<br>11p/XGE3_<br>RXp                   | GND  |

| 9          | GND          | M_PCIE_T<br>X12p/XGE<br>4_TXp<br>/SATA0_T<br>Xp                                                   | M_PCIE_TX<br>12n/XGE4_<br>TXn<br>/SATA0_TX<br>n | GND                                             | GND                                             | M_PCIE_RX<br>12p/XGE4_<br>RXp<br>/SATA0_RX<br>p | M_PCIE_RX<br>12n/XGE4_<br>RXn<br>/SATA0_RX<br>n | GND                                             | GND                                             | GND  |

| 10         | GND          | GND                                                                                               | GND                                             | M_PCIE_TX<br>13p/XGE5_<br>TXp<br>/SATA1_TX<br>p | M_PCIE_TX<br>13n/XGE5_<br>TXn<br>/SATA1_TX<br>n | GND                                             | GND                                             | M_PCIE_RX<br>13p/XGE5_<br>RXp<br>/SATA1_RX<br>p | M_PCIE_RX<br>13n/XGE5_<br>RXn<br>/SATA1_RX<br>n | GND  |

| 11         | GND          | M_PCIE_T<br>X14p/XGE<br>6_TXp<br>/SATA2_T<br>Xp                                                   | M_PCIE_TX<br>14n/XGE6_<br>TXn<br>/SATA2_TX<br>n | GND                                             | GND                                             | M_PCIE_RX<br>14p/XGE6_<br>RXp<br>/SATA2_RX<br>p | M_PCIE_RX<br>14n/XGE6_<br>RXn<br>/SATA2_RX<br>n | GND                                             | GND                                             | GND  |

| 12         | GND          | GND                                                                                               | GND                                             | M_PCIE_TX<br>15p/XGE7_<br>TXp<br>/SATA3_TX<br>p | M_PCIE_TX<br>15n/XGE7_<br>TXn<br>/SATA3_TX<br>n | GND                                             | GND                                             | M_PCIE_RX<br>15p/XGE7_<br>RXp<br>/SATA3_RX<br>p | M_PCIE_RX<br>15n/XGE7_<br>RXn<br>/SATA3_RX<br>n | GND  |

| 13         | GND          | M_HCCS1<br>_RX3p/RF<br>U                                                                          | M_HCCS1_<br>RX3n/RFU                            | GND                                             | GND                                             | M_HCCS1_T<br>X3p/RFU                            | M_HCCS1_<br>TX3n/RFU                            | GND                                             | GND                                             | GND  |

| 14         | GND          | GND                                                                                               | GND                                             | M_HCCS1_<br>RX2p/RFU                            | M_HCCS1_<br>RX2n/RFU                            | GND                                             | GND                                             | M_HCCS1_<br>TX2p/RFU                            | M_HCCS1_<br>TX2n/RFU                            | GND  |

| 15         | GND          | M_HCCS1<br>_RX1p/RF<br>U                                                                          | M_HCCS1_<br>RX1n/RFU                            | GND                                             | GND                                             | M_HCCS1_T<br>X1p/RFU                            | M_HCCS1_<br>TX1n/RFU                            | GND                                             | GND                                             | GND  |

| 16         | GND          | GND                                                                                               | GND                                             | M_HCCS1_<br>RX0p/RFU                            | M_HCCS1_<br>RX0n/RFU                            | GND                                             | GND                                             | M_HCCS1_<br>TX0p/RFU                            | M_HCCS1_<br>TX0n/RFU                            | GND  |

| 17         | GND          | M_HCCS0<br>_RX3p/RF<br>U                                                                          | M_HCCS0_<br>RX3n/RFU                            | GND                                             | GND                                             | M_HCCS0_<br>TX3p/RFU                            | M_HCCS0_<br>TX3n/RFU                            | GND                                             | GND                                             | GND  |

| 18         | GND          | GND                                                                                               | GND                                             | M_HCCS0_<br>RX2p/RFU                            | M_HCCS0_<br>RX2n/RFU                            | GND                                             | GND                                             | M_HCCS0_<br>TX2p/RFU                            | M_HCCS0_<br>TX2n/RFU                            | GND  |

| 19         | GND          | M_HCCS0<br>_RX1p/RF<br>U                                                                          | M_HCCS0_<br>RX1n/RFU                            | GND                                             | GND                                             | M_HCCS0_<br>TX1p/RFU                            | M_HCCS0_<br>TX1n/RFU                            | GND                                             | GND                                             | GND  |

| 20 | GND             | GND                      | GND                  | M_HCCS0_<br>RX0p/RFU | M_HCCS0_<br>RX0n/RFU | GND             | GND               | M_HCCS0_<br>TX0p/RFU | M_HCCS0_<br>TX0n/RFU | GND                   |

|----|-----------------|--------------------------|----------------------|----------------------|----------------------|-----------------|-------------------|----------------------|----------------------|-----------------------|

| 21 | GND             | M_PCIE_T<br>X0n          | M_PCIE_TX<br>0p      | GND                  | GND                  | M_PCIE_RX<br>0p | M_PCIE_RX<br>0n   | GND                  | GND                  | GND                   |

| 22 | GND             | GND                      | GND                  | M_PCIE_TX<br>1n      | M_PCIE_TX<br>1p      | GND             | GND               | M_PCIE_RX<br>1p      | M_PCIE_RX<br>1n      | GND                   |

| 23 | GND             | M_PCIE_T<br>X2n          | M_PCIE_TX<br>2p      | GND                  | GND                  | M_PCIE_RX<br>2p | M_PCIE_RX<br>2n   | GND                  | GND                  | GND                   |

| 24 | GND             | GND                      | GND                  | M_PCIE_TX<br>3n      | M_PCIE_TX<br>3p      | GND             | GND               | M_PCIE_RX<br>3p      | M_PCIE_RX<br>3n      | GND                   |

| 25 | GND             | M_PCIE_T<br>X4n          | M_PCIE_TX<br>4p      | GND                  | GND                  | M_PCIE_RX<br>4p | M_PCIE_RX<br>4n   | GND                  | GND                  | GND                   |

| 26 | GND             | GND                      | GND                  | M_PCIE_TX<br>5n      | M_PCIE_TX<br>5p      | GND             | GND               | M_PCIE_RX<br>5p      | M_PCIE_RX<br>5n      | GND                   |

| 27 | GND             | M_PCIE_T<br>X6n          | M_PCIE_TX<br>6p      | GND                  | GND                  | M_PCIE_RX<br>6p | M_PCIE_RX<br>6n   | GND                  | GND                  | GND                   |

| 28 | GND             | GND                      | GND                  | M_PCIE_TX<br>7n      | M_PCIE_TX<br>7p      | GND             | GND               | M_PCIE_RX<br>7p      | M_PCIE_RX<br>7n      | GND                   |

| 29 | GND             | PCIE_100<br>M_CLKIN<br>n | PCIE_100M<br>_CLKINp | GND                  | GND                  | M_USB_DP        | M_USB_DM          | GND                  | GND                  | GND                   |

| 30 | GND             | GND                      | GND                  | PMU_RSTO<br>UT#      | PMU_RSTI<br>N#       | GND             | GND               | GND                  | S_SYS_RST<br>IN#     | M_PCIERC_<br>SEL#     |

| 31 | M_OS_EXI<br>T   | SPI5_CS0<br>#            | M_UARTD_<br>TX       | M_UARTD_<br>RX       | SPI6_CLK             | SPI6_MOSI       | M_SYS_RS<br>TOUT# | IPMC_I2C2_<br>SCL    | IPMC_I2C2_<br>SDA    | GND                   |

| 32 | RSV             | SPI5_CLK                 | SPI5_MOSI            | M_PCIE_RS<br>TOUT#   | M_MDC1_C<br>LK       | SPI6_CS0#       | M_CAN6_T<br>XD    | M_I2C6_SC<br>L       | GND                  | S_SYS_CLKI<br>N_38M4  |

| 33 | PWR_BT#         | SYS_RUN                  | SPI5_MISO            | M_PCIE_RS<br>TIN#    | M_MDC1_D<br>AT       | SPI6_MISO       | M_CAN6_R<br>XD    | M_I2C6_SD<br>A       | GND                  | M_SYS_CLK<br>OUT_38M4 |

| 34 | M_MDC0_<br>DAT  | M_RSVD_<br>STRAP1        | GND                  | M_UART7_<br>RX       | M_CAN7_R<br>XD       | M_CAN13_T<br>XD | M_CAN4_T<br>XD    | M_CAN5_T<br>XD       | M_UART8_<br>TX       | GND                   |

| 35 | M_MDC0_<br>CLK  | M_RSVD_<br>STRAP4        | M_RSVD_S<br>TRAP0    | M_UART7_<br>TX       | M_CAN7_T<br>XD       | M_CAN13_R<br>XD | M_CAN4_R<br>XD    | M_CAN5_R<br>XD       | M_UART8_<br>RX       | M_HKADC_I<br>N0       |

| 36 | M_TSYNC         | SPI0_MO<br>SI            | SPI0_MISO            | SPI0_CS0#            | SPI0_CLK             | GND             | IPMC_PWM          | RSV                  | M_HKADC_<br>IN1      | M_HKADC_I<br>N2       |

| 37 | M_DUAL_<br>SEL# | SPI1_CLK                 | SPI1_CS0#            | M_UART1_T<br>X       | M_UART2_<br>RX       | M_I2C7_SD<br>A  | M_GPIO25<br>8     | IPMC_UAR<br>TD_RX    | M_MASTER<br>_SEL     | BT_RST#               |

| 38 | M_GPIO2<br>67   | SPI1_MIS<br>O            | SPI1_MOSI            | M_UART1_R<br>X       | M_UART2_<br>TX       | M_I2C7_SC<br>L  | M_GPIO189         | IPMC_UAR<br>TD_TX    | M_GPIO262            | M_GPIO270             |

| 39 | M_I2C5_S<br>CL  | M_I2C4_S<br>CL           | M_XGE3_L<br>ED1      | M_SATA0_<br>LED      | M_XGE2_L<br>ED0      | M_XGE1_LE<br>D1 | M_XGE0_L<br>ED1   | M_GPI0273            | M_GPIO188            | M_GPIO272             |

| 40 | M_I2C5_S<br>DA  | M_I2C4_S<br>DA           | M_SATA3_<br>LED      | M_SATA2_<br>LED      | M_SATA1_<br>LED      | M_XGE2_LE<br>D1 | M_XGE3_L<br>ED0   | M_XGE1_LE<br>D0      | M_XGE0_L<br>ED0      | M_GPIO274             |

信号定义说明

# 信号定义说明

| 序号 | 信号名称                    | 方向  | 电平             | 定义说明                                                                                         |

|----|-------------------------|-----|----------------|----------------------------------------------------------------------------------------------|

| 1  | P12V                    | Р   | 12V            | +12V电源输入,12V±5%,电流≥8A,纹波≤50mV                                                                |

| 2  | P3V3_BAT                | Р   | 3V             | +3V电池输入,+2.7V~+3.3V                                                                          |

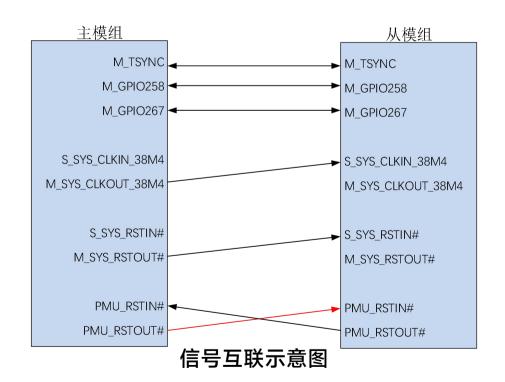

| 3  | M_TSYNC                 | 1/0 | LVCMOS<br>1.8V | 双模组互联同步信号,主模组输出,从模组输入; 单模组时悬空,双模组时<br>互相连接                                                   |

| 4  | M_GPIO258/267           | I/O | LVCMOS<br>1.8V | 双模组互联GPIO信号;单模组时悬空,双模组时互相连接;主模组<br>M_GPIO258从主模组M_GPIO258直连,主模组M_GPIO267从主模组<br>M_GPIO2677直连 |

| 5  | S_SYS_CLKIN_3<br>8M4    | I   | LVCMOS<br>1.8V | 双模组互联时,从模组时钟输入,用于时钟同步,接至主模组的输出时钟,<br>单模组时悬空                                                  |

| 6  | M_SYS_CLKOUT<br>_38M4   | 0   | LVCMOS<br>1.8V | A双模组互联时,主模组时钟输出,用于时钟同步,接至从模组的输入时钟,<br>单模组时悬空                                                 |

| 7  | S_SYS_RSTIN#            | I   | LVCMOS<br>1.8V | 双模组互联时,从模组系统复位输入信号,使用时从模组接主模组到<br>M_SYS_RSTOUT#,主模组复位时,从模组同时进行复位                             |

| 8  | M_SYS_RSTOUT<br>#       | 0   | LVCMOS<br>1.8V | 双模组互联时,主模组系统复位输出信号,主模组连接到从模组<br>S_SYS_RSTIN#引脚,从模组该引脚悬空                                      |

| 9  | PMU_RSTOUT#             | 0   | LVCMOS<br>1.8V | 双模组互联时, PMU复位输出信号,连接到另外一个模组的PMU_RSTIN#<br>引脚,                                                |

| 10 | PMU_RSTIN#              | I   | LVCMOS<br>1.8V | 双模组互联时, PMU复位输入信号,连接另外一个模组的PMU_RSTOUT#<br>引脚                                                 |

| 11 | SPI0~1/SPI5~6           | I/O | LVCMOS<br>1.8V | SPI接口,RC模式时使能,EP模式时不生效                                                                       |

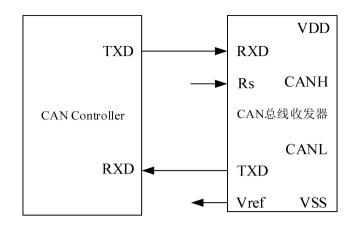

| 12 | M_CAN4/5/6/7/<br>13     | 1/0 | LVCMOS<br>1.8V | CAN接口,RC模式时使能,EP模式时不生效,使用时注意电平转换,增加<br>CAN收发器,CAN7内部与USB复用,使用USB接口时该接口不可用                    |

| 13 | M_I2C4/5/6/7            | I/O | LVCMOS<br>1.8V | I2C MASTER接口,已在模组内4.7K电阻上拉至1.8V,RC模式时使能,EP模式时不生效                                             |

| 14 | M_USB_DP/DM             | I/O |                | USB2.0接口,模组为HOST端,RC模式时使能,EP模式时不生效                                                           |

| 15 | M_UART1/2/7/8_<br>TX/RX | 1/0 | LVCMOS<br>1.8V | UART接口,RC模式时使能,EP模式时不生效                                                                      |

| 16 | M_UARTD                                                        | I/O | LVCMOS<br>3.3V | 310P芯片调试串口                                                                                                                                                                                                                        |

|----|----------------------------------------------------------------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17 | M_MDC0_C<br>LK/DAT                                             | 1/0 | LVCMOS<br>1.8V | MDIO接口,用于XGE接口通过PHY芯片转成电口,RC模式时使能,EP模式时不生效                                                                                                                                                                                        |

| 18 | M_MDC1_C<br>LK/DAT                                             | 1/0 | LVCMOS<br>1.8V | MDIO接口,用于XGE接口通过PHY芯片转成电口,RC模式时使能,EP模式时不生效,该信号为预留功能                                                                                                                                                                               |

| 19 | M_PCIE_TX<br>/RX[7:0]p/n                                       | 1/0 | CML            | PCIE4.0 x8接口,可与M_PCIE_TX/RX[15:8]组成PCIE x16;EP模式时模组为PCIE从设备,RC模式时模组为PCIE HOST端;TX为模组输出,RX为模组输入                                                                                                                                    |

| 20 | M_PCIE_TX<br>/RX[15:8]p/<br>n                                  | 1/0 | CML            | PCIE4.0 x8接口,可与M_PCIE_TX/RX[7:0]组成PCIE x16; EP模式时模组为PCIE从设备,RC模式时模组为PCIE HOST端;接口可复用成XGE、SATA等功能接口;TX为模组输出,RX为模组输入,作为PCIE总线时,TX信号需要在载板上增加0.22uF AC耦合电容;作为XGE接口时,RX信号需要在载板上增加0.01uF AC耦合电容;作为SATA接口时,TX/RX信号需要在载板上增加0.01uF AC耦合电容; |

| 21 | PCIE_100M<br>_CLKINp/n                                         | I   | HCSL           | PCIE参考时钟,EP模式时输入至模组                                                                                                                                                                                                               |

| 22 | PCIE_100M<br>_CLKOUTp/<br>n                                    | 0   | HCSL           | PCIE参考时钟,RC模式时由模组输出                                                                                                                                                                                                               |

| 23 | M_PCIE_RS<br>TIN#                                              | -   | LVCMOS<br>3.3V | PCIE复位信号,EP模式时由HOST输入至模组,RC模式时不生效                                                                                                                                                                                                 |

| 24 | M_PCIE_RS<br>TOUT#                                             | 0   | LVCMOS<br>3.3V | PCIE复位信号,RC模式时由模组输出,EP模式时不生效                                                                                                                                                                                                      |

| 25 | M_HCCS0_<br>TX/RX[3:0]<br>p/n<br>M_HCCS1_<br>TX/RX[3:0]<br>p/n | I/O | CML            | HCCS互联信号,速率24Gbps,用于主从模组互联;TX为模组输出,RX为模组输入                                                                                                                                                                                        |

| 26 | M_HCCS_R<br>EFCLKp/n                                           | I   | CML            | HCCS信号参考时钟,预留使用                                                                                                                                                                                                                   |

| 27 | XGE0~7                                                         | I/O | CML            | 万兆以太网serdes接口,可配置为10G BASE-X;RC模式时可复用为XGE或PCIE host接口,部分接口可复用为SATA接口;EP模式时可配置为PCIE device接口;TX为模组输出,RX为模组输入                                                                                                                       |

| 28 | SATA0~3                                                        | 1/0 | CML            | SATA3.0接口,HOST端;RC模式下可以复用为PCIE host接口、或XGE接口;<br>EP模式时可配置为PCIE device接口;TX为模组输出,RX为模组输入                                                                                                                                           |

| 29 | MASTER_S<br>EL                                                 | I   | LVCMOS<br>1.8V | 模组主模组选择信号,内部有上拉,悬空表示选择为主模组模式,0欧姆电阻接<br>地表示选择为从模组模式;单模组时必须悬空                                                                                                                                                                       |

| 30 | DUAL_SEL<br>#                                                  | I   | LVCMOS<br>1.8V | 模组单模组/双模组选择信号,内部有上拉,悬空表示选择为单模组模式,0欧姆<br>电阻接地表示选择为双模组模式;单模组时必须悬空                                                                                                                                                                   |

| 31 | PCIERC_SE<br>L#                                                | I   | LVCMOS<br>1.8V | 模组PCIE接口RC/EP模式选择信号,内部有上拉,悬空表示选择为EP模式,0欧姆电阻接地表示选择为RC模式;EP模式时必须悬空,双模组互联时,此设置两个模组必须相同,即同为EP或RC                                                                                                                                      |

| 32 | M_OS_EXIT             | 0   | LVCMO<br>S 3.3V | 系统退出标志,RC模式可用,预留                                                         |

|----|-----------------------|-----|-----------------|--------------------------------------------------------------------------|

| 33 | PWR_BT#               | ı   | LVCMO<br>S 3.3V | 外部开关机信号,模组内部已有上拉,低电平有效,短按(≤1s)开机,长按(≥5s)<br>关机,可连接开关机按键,预留功能,暂不使用        |

| 34 | BT_RST#               | I   | LVCMO<br>S 3.3V | 外部复位信号,模组内部已有上拉,低电平有效,可连接复位按键                                            |

| 35 | SYS_RUN               | 0   | LVCMO<br>S 3.3V | LVCMOS 3.3V电平,系统运行指示灯                                                    |

| 36 | M_RSVD_ST<br>RAP4/1/0 | I   | LVCMO<br>S 1.8V | 系统引导方式选择,内部有上拉,RC模式时使用,EP模式时不生效                                          |

| 37 | M_XGE[0:3]_<br>LED0/1 | 0   | LVCMO<br>S 1.8V | 网络指示灯,仅网口0~3支持,M_XGEx_LED0表示在线状态,常亮;<br>M_XGEx_LED1表示ACT状态,无业务时常亮,有业务时闪烁 |

| 38 | M_SATA[0:3]<br>_LED   | 0   | LVCMO<br>S 1.8V | SATA指示灯,SATA ACT LED指示灯信号                                                |

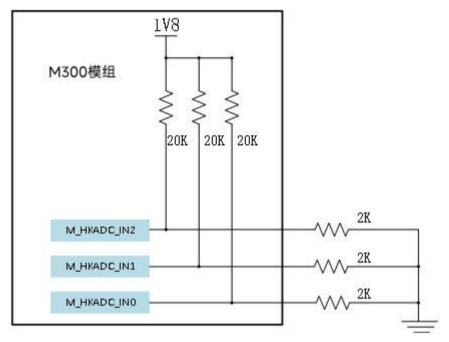

| 39 | M_HKADC_I<br>N[2:0]   | I   | LVCMO<br>S 1.8V | BOARD ID配置引脚,详情见用户指南6.12.2章节                                             |

| 40 | M_GPIOx               | I/O | LVCMO<br>S 1.8V | GPIO接口,RC模式时使能,EP模式时不生效                                                  |

| 41 | IPMC_I2C2             | I/O | LVCMO<br>S 3.3V | IPMC I2C slaver接口,已在模组内4.7K电阻上拉至3.3V                                     |

| 42 | IPMC_UART<br>D        | 1/0 | LVCMO<br>S 3.3V | IPMC调试串口                                                                 |

| 43 | IPMC_PWM              | 0   | LVCMO<br>S 3.3V | IPMC风机PWM接口                                                              |

| 44 | RSV预留引脚               |     |                 | 预留引脚,悬空                                                                  |

# 8接口说明

# 8.1 HCCS接口

AI310SM算力模组定义了两组HCCS X4信号,是模组的直连接口单元,用于模组互联,支持模组之间的低延迟、高带宽和高可靠性的一致性互联。

#### 接口特性如下:

- 1. 支持 2 个模组互联, 实现算力叠加;

- 2. HCCS物理通道不可拆分:

- 3. 信号支持 AC 耦合模式(模组内部已集成AC耦合电容);

- 4. 支持24Gbps/lane,不支持降速使用;

- 5. 不支持 Lane 反转和 Lane 极性反转;

- 6. 100MHz 外部参考时钟;

双模组互联示意图

# 8.1.1 HCCS参考时钟

AI310SM 算力模组HCCS控制器需使用一组外供100MHz差分参考时钟,输入电平类型为CML。

| 模块信号名              | 信号方向  | 信号类型 | 用途/描述                          |

|--------------------|-------|------|--------------------------------|

| M_HCCS_REFC<br>LKp | Input | CML  | HCCS控制器<br>100MHz参考时钟输<br>入P端。 |

| M_HCCS_REFC<br>LKn | Input | CML  | HCCS控制器<br>100MHz参考时钟输<br>入N端。 |

# 时钟信号指标关键规格约束

| 关键规格                          | 规格要求              |

|-------------------------------|-------------------|

| 占空比                           | 50% (±5%)         |

| Trise/Tfall<br>(20%~80%)      | <800ps            |

| 直流偏置电压                        | 650mV~750<br>mV   |

| 100MHz差分<br>参考时钟频偏            | ±1MHz<br>(100MHz) |

| 时钟Buffer时<br>钟源100MHz晶振频<br>偏 | <50ppm            |

# 注意:

- 1. 100MHz参考时钟输入不支持展频。

- 2. 双模组互联时,由载板输入100M参考时钟,且两个算力模组时钟需要同源。

- 3. 100MHz参考时钟需选用AC耦合方式,模组内部已有100nF耦合电容。

- 4. 部分Clock Buffer芯片内部已集成匹配电阻,外部无需增加匹配电阻,选型时请仔细查阅对应芯片的器件手册。

- 5. 参考时钟引脚不使用时,通过50欧姆电阻接地。

- 6. 时钟Buffer输出电平类型支持LVPECL、HCSL、LVDS,设计时可根据所选电平类型搭建外部匹配电路。

常用电平类型匹配电路,可参考下图。

常用电平类型匹配电路

接口说明

# 8.1.2 HCCS数据

| 序号 | 信号名称         | 方向       | 电平类型 | 描述              |

|----|--------------|----------|------|-----------------|

| 1  | M_HCCS0_TX0p | 0        | CML  | HCCS0发送差分数据     |

| 2  | M_HCCS0_TX0n | 0        | CML  | 模组已放置0.22uF耦合电容 |

| 3  | M_HCCS0_TX1p | 0        | CML  |                 |

| 4  | M_HCCS0_TX1n | 0        | CML  |                 |

| 5  | M_HCCS0_TX2p | 0        | CML  |                 |

| 6  | M_HCCS0_TX2n | 0        | CML  |                 |

| 7  | M_HCCS0_TX3p | 0        | CML  |                 |

| 8  | M_HCCS0_TX3n | 0        | CML  |                 |

| 9  | M_HCCS0_RX0p | I        | CML  | HCCS0 接收差分数据    |

| 10 | M_HCCS0_RX0n | I        | CML  |                 |

| 11 | M_HCCS0_RX1p | I        | CML  |                 |

| 12 | M_HCCS0_RX1n | 1        | CML  |                 |

| 13 | M_HCCS0_RX2p | I        | CML  |                 |

| 14 | M_HCCS0_RX2n | 1        | CML  |                 |

| 15 | M_HCCS0_RX3p | 1        | CML  |                 |

| 16 | M_HCCS0_RX3n | 1        | CML  |                 |

| 17 | M_HCCS1_TX0p | 0        | CML  | HCCS1发送差分数据     |

| 18 | M_HCCS1_TX0n | 0        | CML  | 模组已放置0.22uF耦合电容 |

| 19 | M_HCCS1_TX1p | 0        | CML  |                 |

| 20 | M_HCCS1_TX1n | 0        | CML  |                 |

| 21 | M_HCCS1_TX2p | 0        | CML  |                 |

| 22 | M_HCCS1_TX2n | 0        | CML  |                 |

| 23 | M_HCCS1_TX3p | 0        | CML  |                 |

| 24 | M_HCCS1_TX3n | 0        | CML  |                 |

| 25 | M_HCCS1_RX0p | I        | CML  | HCCS1 接收差分数据    |

| 26 | M_HCCS1_RX0n | I        | CML  |                 |

| 27 | M_HCCS1_RX1p | I        | CML  |                 |

| 28 | M_HCCS1_RX1n | I        | CML  |                 |

| 29 | M_HCCS1_RX2p | <u> </u> | CML  |                 |

| 30 | M_HCCS1_RX2n | I        | CML  |                 |

| 31 | M_HCCS1_RX3p | I        | CML  |                 |

| 32 | M_HCCS1_RX3n | I        | CML  |                 |

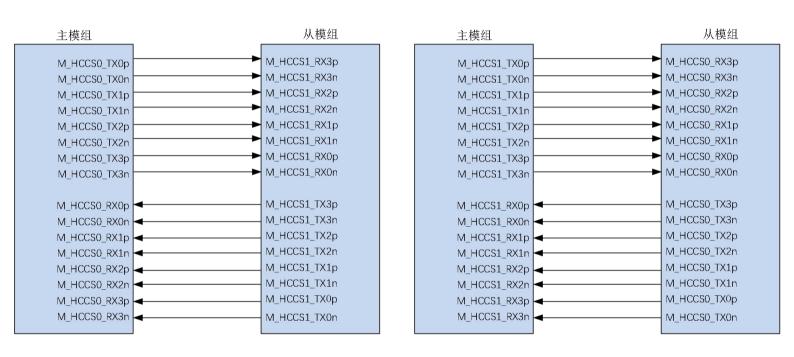

两模组互联时需要交叉连接,即主模组M\_HCCS0\_TXp[3:0]连接从模组M\_HCCS1\_RXp[0:3], 主模组M\_HCCS0\_RXp[3:0]连接从模组M\_HCCS1\_TXp[0:3], 主模组M\_HCCS1\_TXp[3:0]连接从模组M\_HCCS0\_RXp[0:3], 主模组M\_HCCS0\_RXp[3:0]连接从模组M\_HCCS0\_TXp[0:3]。具体连接如下图所示。

HCCS信号互联示意图

注意:不需要双模组互联时,HCCS信号可以悬空。

### 8.1.3 PCB设计

#### 时钟信号

工作速率: 100MHz。

布线长度:根据对端驱动能力决定。

特征阻抗:差分90±10%ohm。

布线等长要求:差分对内±5 mil。

建议布线要求: 时钟信号四周包地处理

#### 数据信号

工作速率: 24Gbps。

布线长度:全链路插损 < -36dB @ 32Gbps(实际请板级考虑高低温对插损的影响)。

特征阻抗: 差分85±10%ohm。

布线等长要求:

- 1) 差分对内±5 mil。

- 2) 差分对间 ball2ball skew: 170 ps。

#### 建议布线要求:

- 1) 差分信号尽量走在内层周围包地,上下相邻层有完整参考地;

- 2) TX与RX尽量分层走线,如果在同一层走线,TX/RX差分对之间必须包地隔离开,要求TX到RX之间的线间距达到6H(H:介质厚度);

- 3) 任意TX或者RX信号所受到的所有串扰和要求小于1.5mV@8GHz, 2mV @16GHz;

# 8.2 SerDes接口

# 8.2.1 参考时钟

AI310SM 算力模组作为EP模式使用时需要外供一组100MHz差分参考时钟,需要与HOST PCIE参考时钟同源,输入电平类型为HCSL。作为RC模式使用时模组对外提供一组100MHz差分参考时钟,用于PCIE外设参考时钟同源,输出电平类型为HCSL。

| 模块信号名            | 信号方向   | 信号类型 | 用途/描述                      |

|------------------|--------|------|----------------------------|

| PCIE_100M_CLKINp | Input  | HCSL | PCIE控制器100MHz<br>参考时钟输入P端。 |

| PCIE_100M_CLKINn | Input  | HCSL | PCIE控制器100MHz<br>参考时钟输入N端。 |

| PCIE_100M_CLKOUT | Output | HCSL | PCIE 100MHz参考时<br>钟输出P端。   |

| PCIE_100M_CLKOUT | Output | HCSL | PCIE 100MHz参考时<br>钟输出N端。   |

#### 时钟信号指标关键规格约束

| 关键规格                          | 规格要求              |

|-------------------------------|-------------------|

| 占空比                           | 50% (±5%)         |

| Trise/Tfall<br>(20%~80%)      | <800ps            |

| 直流偏置电压                        | 650mV~750m<br>V   |

| 100MHz差分<br>参考时钟频偏            | ±1MHz<br>(100MHz) |

| 时钟Buffer时<br>钟源100MHz晶振频<br>偏 | <50ppm            |

## 100MHz参考时钟输入不支持展频。

#### 注:

- 1. 部分Clock Buffer芯片内部已集成匹配电阻,外部无需增加匹配电阻, 选型时请仔细查阅对应芯片的器件手册。

- 2. 参考时钟引脚不使用时,通过50欧姆电阻接地。

# 8.2.2 SerDes数据

| 序号 | 信号名称        | 方向 | 电平类型 | 描述                |

|----|-------------|----|------|-------------------|

| 1  | M_PCIE_TX0p | 0  | CML  | SerDes 发送差分数据0-7  |

| 2  | M_PCIE_TX0n | 0  | CML  | - 模组已放置0.22uF耦合电容 |

| 3  | M_PCIE_TX1p | 0  | CML  |                   |

| 4  | M_PCIE_TX1n | 0  | CML  |                   |

| 5  | M_PCIE_TX2p | 0  | CML  |                   |

| 6  | M_PCIE_TX2n | 0  | CML  |                   |

| 7  | M_PCIE_TX3p | 0  | CML  |                   |

| 8  | M_PCIE_TX3n | 0  | CML  |                   |

| 9  | M_PCIE_TX4p | 0  | CML  |                   |

| 10 | M_PCIE_TX4n | 0  | CML  |                   |

| 11 | M_PCIE_TX5p | 0  | CML  | ]                 |

| 12 | M_PCIE_TX5n | 0  | CML  |                   |

| 13 | M_PCIE_TX6p | 0  | CML  |                   |

| 14 | M_PCIE_TX6n | 0  | CML  |                   |

| 15 | M_PCIE_TX7p | 0  | CML  |                   |

| 16 | M_PCIE_TX7n | 0  | CML  |                   |

| 17 | M_PCIE_RX0p | I  | CML  | SerDes 接收差分数据0-7  |

| 18 | M_PCIE_RX0n | I  | CML  |                   |

| 19 | M_PCIE_RX1p | I  | CML  |                   |

| 20 | M_PCIE_RX1n | I  | CML  |                   |

| 21 | M_PCIE_RX2p | I  | CML  |                   |

| 22 | M_PCIE_RX2n | I  | CML  |                   |

| 23 | M_PCIE_RX3p | I  | CML  |                   |

| 24 | M_PCIE_RX3n | I  | CML  |                   |

| 25 | M_PCIE_RX4p | I  | CML  | ]                 |

| 26 | M_PCIE_RX4n | I  | CML  | ]                 |

| 27 | M_PCIE_RX5p | I  | CML  | ]                 |

| 28 | M_PCIE_RX5n | I  | CML  | ]                 |

| 29 | M_PCIE_RX6p | I  | CML  | ]                 |

| 30 | M_PCIE_RX6n | I  | CML  | ]                 |

| 31 | M_PCIE_RX7p | I  | CML  | ]                 |

| 32 | M_PCIE_RX7n | I  | CML  |                   |

| 41310SM | datasheet                           |   |                | 1女口 奶奶                                                                          |

|---------|-------------------------------------|---|----------------|---------------------------------------------------------------------------------|

| 33      | M_PCIE_TX8p/XGE0_TXp                | 0 | CML            | SerDes发送差分数据8-11<br>复用为PCIE时,需要放置0.22uF耦合                                       |

| 34      | M_PCIE_TX8n/XGE0_TXn                | 0 | CML            | 电容;                                                                             |

| 35      | M_PCIE_TX9p/XGE1_TXp                | 0 | CML            | 00,                                                                             |

| 36      | M_PCIE_TX9n/XGE1_TXn                | 0 | CML            |                                                                                 |

| 37      | M_PCIE_TX10p/XGE2_TXp               | 0 | CML            |                                                                                 |

| 38      | M_PCIE_TX10p/XGE2_TXp               | 0 | CML            |                                                                                 |

| 39      |                                     | 0 | CML            |                                                                                 |

|         | M_PCIE_TX11p/XGE3_TXp               | 0 | CML            |                                                                                 |

| 40      | M_PCIE_TX11n/XGE3_TXn               | 0 | CML            |                                                                                 |

| 41      | M_PCIE_RX8p/XGE0_RXp                | I | CML            | SerDes 接收差分数据8-11<br>复用为XGE时,需要放置0.01uF耦合电                                      |

| 42      | M_PCIE_RX8n/XGE0_RXn                | I | CML            | │ 容;                                                                            |

| 43      | M_PCIE_RX9p/XGE1_RXp                | 1 | CML            |                                                                                 |

| 44      | M_PCIE_RX9n/XGE1_RXn                | 1 | CML            |                                                                                 |

| 45      | M_PCIE_RX10p/XGE2_RXp               | Ī | CML            |                                                                                 |

| 46      | M_PCIE_RX10n/XGE2_RXn               | i | CML            |                                                                                 |

| 47      | M_PCIE_RX11p/XGE3_RXp               | i | CML            |                                                                                 |

| 48      |                                     | 1 | CML            |                                                                                 |

| 48      | M_PCIE_RX11n/XGE3_RXn               | ' | CML            |                                                                                 |

| 49      | M_PCIE_TX12p/XGE4_TXp/SATA0_TXp     | 0 | CML            | SerDes 发送差分数据12-15<br>复用为PCIE时,需要放置0.22uF耦合<br>电容;<br>复用为SATA时,需要放置0.01uF耦合     |

| 50      | M_PCIE_TX12n/XGE4_TXn/<br>SATA0_TXn | 0 | CML            | . 电容<br>                                                                        |

| 51      | M_PCIE_TX13p/XGE5_TXp/<br>SATA1_TXp | 0 | CML            |                                                                                 |

| 52      | M_PCIE_TX13n/XGE5_TXn/ SATA1_TXn    | 0 | CML            |                                                                                 |

| 53      | M_PCIE_TX14p/XGE6_TXp/<br>SATA2_TXp |   | CML            |                                                                                 |

| 54      | M_PCIE_TX14n/XGE6_TXn/<br>SATA2_TXn |   | CML            |                                                                                 |

| 55      | M_PCIE_TX15p/XGE7_TXp/<br>SATA3_TXp |   | CML            |                                                                                 |

| 56      | M_PCIE_TX15n/XGE7_TXn/<br>SATA3_TXn |   | CML            |                                                                                 |

| 57      | M_PCIE_RX12p/XGE4_RXp/SATA0_RX<br>p | 0 | CML            | SerDes 接收差分数据12-15<br>复用为SATA时,需要放置0.01uF耦合<br>电容<br>复用为XGE时,需要放置0.01uF耦合电<br>容 |

| 58      | M_PCIE_RX12n/XGE4_RXn/<br>SATA0_RXn | 0 | CML            |                                                                                 |

| 59      | M_PCIE_RX13p/XGE5_RXp/<br>SATA1_RXp | 0 | CML            |                                                                                 |

| 60      | M_PCIE_RX13n/XGE5_RXn/<br>SATA1_RXn | 0 | CML            |                                                                                 |

| 61      | M_PCIE_RX14p/XGE6_RXp/<br>SATA2_RXp | 0 | CML            |                                                                                 |

| 62      | M_PCIE_RX14n/XGE6_RXn/<br>SATA2_RXn | 0 | CML            |                                                                                 |

| 63      | M_PCIE_RX15p/XGE7_RXp/<br>SATA3_RXp | 0 | CML            |                                                                                 |

| 64      | M_PCIE_RX15n/XGE7_RXn/<br>SATA3_RXn | 0 | CML            |                                                                                 |

| 65      | M_PCIE_RSTIN#                       | I | LVCOMS<br>3.3V | EP模式输入PCIE复位信号,由PCIE<br>HOST提供                                                  |

| 66      | M_PCIE_RSTOUT#                      | 0 | LVCOMS         |                                                                                 |

|         |                                     |   | 3.3V           | 设复位使用                                                                           |

Al310SM datasheet 接口说明

可以根据Board ID选择SerDes应用模式

当作为EP模式时SerDes只能作为PCIE接口使用,支持PCIE 4.0 X16,可以降速降lane使用,此时Board ID需要配置为201。

#### 注意:

- 1. PCIe的lane顺序可以翻转: PCIE支持硬件自适应lane序翻转。

- 2. 所有的lane都支持极性反转。PCIE协议支持极性翻转,能够对外部的极性翻转进行自适应适配。

- 3. 最高支持PCIE 4.0,向下兼容PCIE 3.0 /PCIE 2.0/ PCIE 1.0。

- 4. 最高支持PCIE X16,向下兼容PCIE X8/X4/X2。

- 5. 对于不使用的lane,可以悬空。

当作为RC模式时M\_PCIE\_TX/RX[7:0]只能作为PCIE接口使用,但M\_PCIE\_TX/RX[11:8]可复用为PCIE或XGE接口,M\_PCIE\_TX/RX[15:9]可复用为PCIE、XGE、SATA接口,此时Board ID需要根据具体应用场景进行配置。

|          | 端口名                                   | 规格              | LINE        | 201     | 202    | 203    | 204    | 205      | 206       | 207    | 208    | 209    | 210    | 211    | 212    | 213    | 214    | 215    | 216    |

|----------|---------------------------------------|-----------------|-------------|---------|--------|--------|--------|----------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

|          |                                       |                 | PCIe lane0  |         |        |        |        | PCIEX2   | PCIEX2    |        |        |        | PCIEX2 | PCIEX2 |        |        |        | PCIEX2 | PCIEX2 |

|          |                                       |                 | PCIe lane1  |         |        |        |        | 11111111 | .,,,,,,,, |        |        |        |        |        |        |        |        |        |        |

|          |                                       |                 | PCIe lane2  |         |        | PCIEX4 | PCIEX4 | PCIEX2   | PCIEX2    |        | PCIEX4 | PCIEX4 | PCIEX2 | PCIEX2 |        | PCIEX4 | PCIEX4 | PCIEX2 | PCIEX2 |

|          |                                       |                 | PCIe lane3  |         |        |        |        |          |           |        |        |        |        |        |        |        |        |        |        |

|          | M_PCIE_TX/RX[7:0]                     | x8              | PCIe lane4  |         | PCIEX8 |        | PCIEX2 |          | PCIEX2    | PCIEX8 |        | PCIEX2 |        | PCIEX2 | PCIEX8 |        | PCIEX2 |        | PCIEX2 |

|          | (PCIE)                                |                 | PCIe lane5  |         |        |        |        |          |           |        |        |        |        |        |        |        |        |        |        |

|          |                                       |                 | PCIe lane6  |         |        | PCIEX4 | PCIEX2 | PCIEX4   | PCIEX2    | PCIEX4 | PCIEX2 | PCIEX4 | PCIEX2 |        | PCIEX4 | PCIEX2 | PCIEX4 | PC1EX2 |        |

| RC       |                                       |                 | PCIe lane7  | PCIEX16 |        |        |        |          |           |        |        |        |        |        |        |        |        |        |        |

| New York |                                       |                 | PCIe lane8  |         |        |        |        |          |           | XGEO   | XGEO   | XGE0   | XGEO   | XGEO   | XGE0   | XGEO   | XGE0   | XGEO   | XGEO   |

|          | M_PCIE_TX/RX[11:8]                    | x4              | PCIe lane9  |         |        |        |        |          |           | XGE1   |

|          | (PCIE;XGE)                            |                 | PCIe lane10 |         |        |        |        |          | XGE2      | XGE2   | XGE2   | XGE2   | XGE2   | XGE2   | XGE2   | XGE2   | XGE2   | XGE2   |        |

|          |                                       |                 | PCIe lane11 |         |        |        |        |          |           | XGE3   |

|          |                                       |                 | PCIe lane12 |         | PCIEX8 | PCIEX8 | PCIEX8 | PCIEX8   | PCIEX8    | XGE4   | XGE4   | XGE4   | XGE4   | XGE4   | SATA0  | SATA0  | SATA0  | SATAO  | SATAO  |

|          |                                       |                 | PCIe lane13 |         |        |        |        |          |           | XGE5   | XGE5   | XGE5   | XGE5   | XGE5   | SATA1  | SATA1  | SATA1  | SATA1  | SATA1  |

|          | M_PCIE_TX/RX[15:9]<br>(PCIE,XGE:SATA) | x4              | PCIe lane14 |         |        |        |        |          |           | XGE6   | XGE6   | XGE6   | XGE6   | XGE6   | SATA2  | SATA2  | SATA2  | SATA2  | SATA2  |

|          | (I CILAGE, SATA)                      | (PCIE,AGE,SATA) | PCIe lane15 |         |        |        |        |          |           | XGE7   | XGE7   | XGE7   | XGE7   | XGE7   | SATA3  | SATA3  | SATA3  | SATA3  | SATA3  |

- 1. PCIe的lane顺序可以翻转; PCIE支持硬件自适应lane序翻转;

- 2. 所有的lane都支持极性反转。PCIE协议支持极性翻转,能够对外部的极性翻转进行自适应适配,SATA/XGE不支持自适应的极性翻转。

- 3. 对于不使用的lane,可以悬空。

## 8.2.3 PCB设计

#### 时钟信号

工作速率: 100MHz。

布线长度:根据对端驱动能力决定。

特征阻抗:差分100±10%ohm。

布线等长要求:差分对内±5 mil。

建议布线要求: 时钟信号四周包地处理

#### 数据信号

工作速率: PCIE 4.0。

布线长度:全链路插损(bump2bump) < -28dB/8GHz(实际请板级考虑高低温对插损的影响)。

特征阻抗:差分85±10%ohm。

布线等长要求:

- 1) 差分对内保证等长:作为EP,板级误差2.5mil;作为RC,板级误差5mil;

- 2) TX差分对之间, skew要求小于200ps

- 3) RX差分对之间,skew要求小于200ps

- 4) TX/RX对间不要求等长

#### 建议布线要求:

- 1) 差分信号尽量走在内层周围包地,上下相邻层有完整参考地;

- 2) TX与RX尽量分层走线,如果在同一层走线,TX/RX差分对之间必须包地隔离开,要求TX到RX之间的线间距达到6H(H:介质厚度);

- 3) 任意TX或者RX信号所受到的所有串扰和要求小于1.5mV@8GHz, 2mV @16GHz:

### 8.3 SPI接口

### 8.3.1 SPI数据

AI310SM算力模组提供了4组SPI总线接口,IO电平为LVCMOS 1.8V,SPI接口仅在RC模式下可用。可以作为一个主设备与外部的设备来进行同步串行通信,主要应用于外接触摸屏、SD卡、WIFI和TPM等。

#### SPI接口具有以下特性:

- 1) 支持串行主设备操作:

- 2) 支持可编程数据传输速率,传输速率配置范围为200MHz/N(8<=N<=65534, 偶数),最高传输速率25MHz;

- 3) 支持MSTR/SLV操作,静态切换,在MSTR模式下,每个SPI控制器支持最大4个Slave;

- 4) 支持接口时钟频率可编程:

- 5) 收/发为分开的32bits宽、深度为64的FIFO(发送FIFO和接收FIFO各一个), 支持FIFO禁止或使能;

- 6) 串行数据序列为先MSB, 后LSB;

- 7) 支持三种帧格式: Motorola SPI、National Microwire、TI SSP;

- 8) 支持各种帧格式静态切换;

- 9) 数据帧大小可编程: 4bit~32bit;

- 10) 支持每个片选的有效极性可配置;

- 11) 支持一个组合中断连接到中断控制器,中断类型包括:接收FIFO中断、发送 FIFO中断、传输冲突中断;

- 12) 支持初始中断状态查询和屏蔽后中断状态查询;

- 13) 支持关断SPI接口时钟以节省功耗;

- 14) 内部提供环回测试模式;

- 15) Motorola SPI帧格式时,串行时钟相位可配置;SPI传输时数据跟时钟的关系 支持软件可配。

| 序号  | 信号名称         | 方向   | IO电平           | 描述                      |

|-----|--------------|------|----------------|-------------------------|

| 1   | SPI0_CLK     | I/O  | LVCMOS         | SPI0时钟信号                |

| 1   |              |      | 1.8V           | 支持主从模式                  |

|     | SPI0_CS0#    | I/O  | LVCMOS         | SPI0片选信号                |

| 2   |              |      | 1.8V           | 支持主从模式                  |

|     | SPI0_MOSI    | I/O  | LVCMOS         | SPIO数据输出信号              |

| 3   | _            |      | 1.8V           | 支持主从模式                  |

|     | SPI0_MISO    | I/O  | LVCMOS         | SPIO数据输入信号              |

| 4   | _            |      | 1.8V           | 支持主从模式                  |

|     | SPI1_CLK     | 1/0  | LVCMOS         | SPI1时钟信号                |

| 5   |              |      | 1.8V           | 支持主从模式                  |

|     | SPI1_CS0#    | 1/0  | LVCMOS         | SPI1片选信号                |

| 6   | GGGG         |      | 1.8V           | 支持主从模式                  |

|     | SPI1_MOSI    | I/O  | LVCMOS         | 文符主从模式<br>  SPI1数据输出信号  |

| 7   | 01 H_1 1001  | ., 0 | 1.8V           |                         |

|     | SPI1 MISO    | 1/0  | LVCMOS         | 支持主从模式<br>SPI1数据输入信号    |

| 8   | 31 11_111130 | "    | 1.8V           |                         |

|     | SPI5_CLK     | 1/0  | LVCMOS         | 支持主从模式<br>SPI5时钟信号      |

| 9   | SFIS_CLIX    | 1/0  | 1.8V           |                         |

|     | SPI5 CS0#    | I/O  | LVCMOS         | 支持主从模式可配置<br>SPI5片选信号   |

| 10  | 3PI5_C3U#    | 1/0  | 1.8V           |                         |

|     | CDIE MOCI    | 1/0  |                | 支持主从模式可配置<br>SPI5数据输出信号 |

| 11  | SPI5_MOSI    | I/O  | LVCMOS<br>1.8V |                         |

|     | ODIE MICO    | 1/0  |                | 支持主从模式可配置               |

| 12  | SPI5_MISO    | I/O  | LVCMOS<br>1.8V | SPI5数据输入信号              |

|     | 001/ 011/    | 1/2  |                | 支持主从模式可配置               |

| 13  | SPI6_CLK     | 1/0  | LVCMOS<br>1.8V | SPI6时钟信号                |

|     |              |      |                | 支持主从模式可配置               |

| 14  | SPI6_CS0#    | I/O  | LVCMOS         | SPI6片选信号                |

| 1-7 |              |      | 1.8V           | 支持主从模式可配置               |

| 15  | SPI6_MOSI    | 1/0  | LVCMOS         | SPI6数据输出信号              |

| 13  |              |      | 1.8V           | 支持主从模式可配置               |

| 16  | SPI6_MISO    | 1/0  | LVCMOS         | SPI6数据输入信号              |

| 10  |              |      | 1.8V           | 支持主从模式可配置               |

- 1. SPI工作时,通过片选信号来选择相应的从机;

- 2. 进行同步串行数据传输时SPI按照数据高位在前,低位在后的方式传输;

- 3. 使用时注意电平匹配;

- 4. CLK串联22ohm, Data直连(建议预留0欧姆串联电阻);

- 5. SPI不使用, 引脚悬空即可;

# 8.3.2 PCB设计

工作速率: 25MHz。

布线长度: 走线长度< 10 inch。

特征阻抗: 40~50ohm。

## 8.4 CAN 接口

AI310SM算力模组提供了5组CAN总线接口,IO电平为LVCMOS 1.8V,CAN接口仅在RC模式下可用。其中CAN7内部与USB复用,使用USB接口时该接口不可用。

| 序号 | 信号名称        | 方向 | IO电平        | 描述          |

|----|-------------|----|-------------|-------------|

| 1  | MCAN4_RXD   | I  | LVCMOS 1.8V | CAN4的接收数据线  |

| 2  | M_CAN4_TXD  | 0  | LVCMOS 1.8V | CAN4的发送数据线  |

| 3  | MCAN5_RXD   | I  | LVCMOS 1.8V | CAN5的接收数据线  |

| 4  | M_CAN5_TXD  | 0  | LVCMOS 1.8V | CAN5的发送数据线  |

| 5  | MCAN6_RXD   | I  | LVCMOS 1.8V | CAN6的接收数据线  |

| 6  | M_CAN6_TXD  | 0  | LVCMOS 1.8V | CAN6的发送数据线  |

| 7  | M_CAN7_RXD  | I  | LVCMOS 1.8V | CAN7的接收数据线  |

| 8  | M_CAN7_TXD  | 0  | LVCMOS 1.8V | CAN7的发送数据线  |

| 9  | M_CAN13_RXD | I  | LVCMOS 1.8V | CAN13的接收数据线 |

| 10 | M_CAN13_TXD | 0  | LVCMOS 1.8V | CAN13的发送数据线 |

CAN接口可以与具有 CAN 接口的设备通讯,也可以多个芯片组成控制网络,完成信息的传输、交互和控制功能。

CAN的典型应用框图

#### 注意:

- 1. 使用时需要增加CAN收发器;

- 2. 使用时注意电平匹配;

- 3. 不使用时, 引脚悬空即可;

# 8.5 UART接口

AI310SM算力模组提供了5组UART接口。其中M\_UARTD为310P调试串口,电平为LVCMOS 3.3V; M\_UART1/2/7/8为业务串口,电平为LVCMOS 1.8V, 且仅在RC模式下可用。

UART异步串行的通信接口,主要执行串并转换功能,将芯片发送到外围设备的数据进行并串转换,同时将来自外围设备的串行数据进行串并转换。该接口模块遵循 RS232 串行通信协议。业务UART具有以下特点:

- 1) 支持8 bits 宽、深度为 32 的发送 FIFO 和 12 bits 宽、深度为 32 的接收 FIFO, 支持 FIFO 禁止或使能;

- 2) 支持5/6/7/8 bits 可编程数据位:

- 3) 支持1/2 bits 可编程停止位:

- 4) 支持奇、偶校验方式,支持无校验位,支持校验位固定为软件设定值;

- 5) 支持传送速率可编程,传送速率范围为: UART 总线时钟频率/(16×N) (0<N<65536, N 为整数, UART 总线时钟频率单位为Hz);

- 6) 支持一个组合中断连接到中断控制器,中断类型包括:接收FIFO中断、 发送 FIFO中断、接收超时中断、帧格式错误中断、帧校验错误中断、 传输中止中断;

- 7) 支持初始中断状态查询和屏蔽后中断状态查询;

- 8) 支持关断UART 接口时钟以节省功耗;

- 9) 支持主从模式, 9 bits UART。

| 序号 | 信号名称       | 方向 | IO电平        | 描述                   |

|----|------------|----|-------------|----------------------|

| 1  | M_UART1_RX | I  | LVCMOS 1.8V | UART1的接收数据线,模组内有上拉电阻 |

| 2  | M_UART1_TX | 0  | LVCMOS 1.8V | UART1的发送数据线          |

| 3  | M_UART2_RX | I  | LVCMOS 1.8V | UART2的接收数据线,模组内有上拉电阻 |

| 4  | M_UART2_TX | 0  | LVCMOS 1.8V | UART2的发送数据线          |

| 5  | M_UART7_RX | I  | LVCMOS 1.8V | UART7的接收数据线,模组内有上拉电阻 |

| 6  | M_UART7_TX | 0  | LVCMOS 1.8V | UART7的发送数据线          |

| 7  | M_UART8_RX | I  | LVCMOS 1.8V | UART8的接收数据线,模组内有上拉电阻 |

| 8  | M_UART8_TX | 0  | LVCMOS 1.8V | UART8的发送数据线          |

| 9  | M_UARTD_RX | I  | LVCMOS 3.3V | 310P调试串口的接收数据线,模组内有上 |

| 9  |            |    |             | 拉电阻                  |

| 10 | M_UARTD_TX | 0  | LVCMOS 3.3V | 310P调试串口的发送数据线       |

- 1. 使用时注意电平匹配;

- 2. 不使用时, 引脚悬空即可;

- 3.调试串口波特率115200bps, 8位数据为, 1位停止位, 无奇偶校验位

# 8.6 I2C接口

AI310SM算力模组提供了4组I2C总线接口,IO 电平为LVCOMS 1.8V,仅在RC模式下可用。实现标准I2C主设备功能,兼容Philips I2C总线协议,可完成对I2C总线上的从设备的数据发送和接收。主要用于音视频A/D、D/A等外部I2C器件的控制。

#### 通用I2C接口具有以下特点:

- 1) 支持标准I2C总线协议;

- 2) 仅支持主设备操作:

- 3) 支持7bit和10bit从设备地址;

- 4) 支持可编程时钟,可实现通讯速率控制,支持100KHz、400KHz等常规速率,ISP内I2C 6/7支持1MHz;

- 5) I2C\_DELAY功能可将I2C\_SDA信号输出最大延迟约300ns,软件可配

| 序号 | 信号名称       | 方向  | IO电平        | 描述                         |

|----|------------|-----|-------------|----------------------------|

|    |            |     |             |                            |

| 1  | M_I2C4_SCL | I/O | LVCMOS 1.8V | I2C4时钟,模组内部已有2.2K电阻上拉到1.8V |

| 2  | M_I2C4_SDA | 1/0 | LVCMOS 1.8V | I2C4数据,模组内部已有2.2K电阻上拉到1.8V |

| 3  | M_I2C5_SCL | 1/0 | LVCMOS 1.8V | I2C5时钟,模组内部已有2.2K电阻上拉到1.8V |

| 4  | M_I2C5_SDA | 1/0 | LVCMOS 1.8V | I2C5数据,模组内部已有2.2K电阻上拉到1.8V |

| 5  | M_I2C6_SCL | 1/0 | LVCMOS 1.8V | I2C6时钟,模组内部已有2.2K电阻上拉到1.8V |

| 6  | M_I2C6_SDA | 1/0 | LVCMOS 1.8V | I2C6数据,模组内部已有2.2K电阻上拉到1.8V |

| 7  | M_I2C7_SCL | 1/0 | LVCMOS 1.8V | I2C7时钟,模组内部已有2.2K电阻上拉到1.8V |

| 8  | M_I2C7_SDA | 1/0 | LVCMOS 1.8V | I2C7数据,模组内部已有2.2K电阻上拉到1.8V |

- 1. 仅支持主模式, 使用时注意电平匹配;

- 2. 不使用时, 引脚悬空即可;

# 8.7 USB接口

### 8.7.1 USB数据

AI310SM算力模组提供了1路标准USB2.0接口,仅在RC模式下可用。

| 序号 | 信号名称     | 方向  | IO电平 | 描述           |

|----|----------|-----|------|--------------|

| 1  | M_USB_DP | 1/0 | 1    | USB2.0差分数据p端 |

| 2  | M_USB_DM | 1/0 | 1    | USB2.0差分数据端  |

#### 注意:

- 1) 仅在RC模式下可用,但目前华为未开放该功能;

- 2) 不使用时, 引脚悬空即可;

## 8.7.2 PCB设计

工作速率: 480Mbps。

布线长度:链路长度<5 inch。

特征阻抗:差分90±10%ohm。

布线等长要求: 差分对内等长控制在5 mil以内;

建议布线要求:

- 1) 尽量少打孔, 打孔换层时必须对称, 打孔换层时, 需加回流地孔。

- 2) 远离电源,时钟等干扰信号,包地处理。

Al310SM datasheet 接口说明

## 8.8 MDIO接口

#### 8.8.1 MDIO

AI310SM算力模组提供了2路MDIO接口,仅在RC模式下可用。MDIO是对外部以太网接口的 PHY 芯片进行配置和管理的接口控制模块,软件可以通过配置 MDIO 相应的寄存器实现对 PHY 芯片内部寄存器的读写,最终实现对 PHY 芯片的控制和管理。例如复位控制、自环控制、速度选择、双工选择、冲突测试、自协商使能、物理层状态获取等等。

#### MDIO 接口具有以下特件:

- 1. 支持2 个独立的 MDIO 接口;

- 每个MDIO 接口可独立配置为支持 IEEE802.3 协议的 Clause22 章节或 Clause45 章节;

- 3. 支持MDIO 接口时序,MDIO 时钟频率支持两个频点, 2.5MHz、2MHz可选;

- 4. 支持对PHY内部寄存器的读写访问、PHY 地址、寄存器地址等可配置;

- 5. 支持对GE PHY 内部寄存器的自动查询,每个 MDIO 接口最大 支持 5 个 PHY 器件的状态查询,PHY状态改变则上报中断 (每个配置的 PHY 地址可以监控指定最多 2个地址寄存器的 任意指定位状态值是否发生改变)。

| 序号 | 信号名称           | 方向  | IO电平        | 描述                           |

|----|----------------|-----|-------------|------------------------------|

| 1  | M_MDC0_CLK     | 0   | LVCMOS 1.8V | MDIO0 时钟信号,模组内部已有1K电阻上拉到1.8V |

| 2  | M_MDC0_DA<br>T | 1/0 | LVCMOS 1.8V | MDIO0 数据信号,模组内部已有1K电阻上拉到1.8V |

| 3  | M_MDC1_CLK     | 0   | LVCMOS 1.8V | MDIO1 时钟信号,模组内部已有1K电阻上拉到1.8V |

| 4  | M_MDC1_DAT     | 1/0 | LVCMOS 1.8V | MDIO1 数据信号,模组内部已有1K电阻上拉到1.8V |

### 注意:

- 1. MDIO接口与外部PHY连接时,只需将两者的时钟线和数据线分别对接即可;

- 2. 目前只有MDC0接口可用;

- 3. 使用时注意点评匹配;

- 4. 不使用时, 引脚悬空即可;

# 8.8.2 PCB设计

工作速率: 12.5MHz(typ:2.5MHz)。

布线长度: 链路长度<15 inch。

特征阻抗: 40~50ohm。

布线等长要求: 无严格等长约束, MDC/MDIO 一起走线;

建议布线要求:建议与其他接口信号包地隔离。

# 8.9 LED信号

AI310SM算力模组提供了4组XGE网口指示灯,仅网口0~3支持;提供4个SATA指示灯总线接口;同时提供一个运行指示灯。

| 序号 | 信号名称        | 方向 | IO电平        | 描述                                |

|----|-------------|----|-------------|-----------------------------------|

| 1  | M XGE0 LED0 | 0  | LVCMOS 1.8V | XGE0在线状态,常亮                       |

|    |             |    |             |                                   |

| 2  | M_XGE0_LED1 | 0  | LVCMOS 1.8V | XGEO Activity状态,无业务时常亮,有业务时闪<br>烁 |

| 3  | M_XGE1_LED0 | 0  | LVCMOS 1.8V | XGE1在线状态,常亮                       |

| 4  | M_XGE1_LED1 | 0  | LVCMOS 1.8V | XGE1 Activity状态,无业务时常亮,有业务时闪<br>烁 |

| 5  | M_XGE2_LED0 | 0  | LVCMOS 1.8V | XGE2在线状态,常亮                       |

| 6  | M_XGE2_LED1 | 0  | LVCMOS 1.8V | XGE2 Activity状态,无业务时常亮,有业务时闪<br>烁 |

| 7  | M_XGE3_LED0 | 0  | LVCMOS 1.8V | XGE3在线状态,常亮                       |

| 8  | M_XGE3_LED1 | 0  | LVCMOS 1.8V | XGE3 Activity状态,无业务时常亮,有业务时闪<br>烁 |

| 9  | M_SATA0_LED | 0  | LVCMOS 1.8V | SATA PORTO Activity LED点灯信号。      |

| 10 | M_SATA1_LED | 0  | LVCMOS 1.8V | SATA PORT1 Activity LED点灯信号。      |

| 11 | M_SATA2_LED | 0  | LVCMOS 1.8V | SATA PORT2 Activity LED点灯信号。      |

| 12 | M_SATA3_LED | 0  | LVCMOS 1.8V | SATA PORT3 Activity LED点灯信号。      |

| 13 | SYS_RUN     | 0  | LVCMOS 3.3V | 模组运行时处于闪烁状态                       |

- 1. SATA一般命令或者NCQ命令正在执行、未完成时,SATAx\_LED输出高电平。

- 2. 使用时注意电平匹配。

- 3. 接口不使用, 引脚悬空处理即可。

#### 8.10 **GPIO**

AI310SM算力模组提供了7个通用GPIO接口,仅在RC模式下可用。

#### GPIO具有以下特点:

- 1. 支持对串行及低于32bit的并行数据总线进行模拟;

- 2. 每个信号有各自的数据寄存器和数据流方向寄存器:

- 3. 支持初始中断状态查询和屏蔽后中断状态查询;

- 4. 当每一组有多个中断同时发生的时候,将会统一汇集成一个中断进行上报;

- 5. GPIO\_INTTYPE\_LEVEL(中断类型寄存器)和GPIO\_INT\_POLARITY(中断触发极性控制寄存器)两个寄存器共同决定了中断源的特性和中断触发类别,中断支持电平和双沿触发:

- 6. GPIO作为输入管脚时,可作为中断源,每个GPIO管脚具有独立的中断控制;

- 7. GPIO作为输出管脚时,每个GPIO管脚支持独立使能或关闭;

| 序号 | 信号名称      | 方向  | IO电平        | 描述     |

|----|-----------|-----|-------------|--------|

| 1  | M_GPIO188 | 1/0 | LVCMOS 1.8V | 通用GPIO |

| 2  | M_GPIO189 | 1/0 | LVCMOS 1.8V | 通用GPIO |

| 3  | M_GPIO262 | 1/0 | LVCMOS 1.8V | 通用GPIO |

| 4  | M_GPIO270 | 1/0 | LVCMOS 1.8V | 通用GPIO |

| 5  | M_GPIO272 | 1/0 | LVCMOS 1.8V | 通用GPIO |

| 6  | M_GPIO273 | 1/0 | LVCMOS 1.8V | 通用GPIO |

| 7  | M_GPIO274 | I/O | LVCMOS 1.8V | 通用GPIO |

- 1. 使用时注意电平匹配。

- 2. 接口不使用, 引脚悬空处理即可。

# 8.11 双模组互联信号

AI310SM算力模组提供双模组互联信号,包括GPIO信号、复位信号以及时钟信号。

| 序号 | 信号名称            | 方向  | IO电平   | 描述         |

|----|-----------------|-----|--------|------------|

| 1  | M_TSYNC         | 1/0 | LVCMOS | 互联同步信号     |

| 1  |                 |     | 1.8V   |            |

| 2  | M_GPIO258       | 1/0 | LVCMOS | 互联同步GPIO   |

|    |                 |     | 1.8V   |            |

| 3  | M_GPIO267       | 1/0 | LVCMOS | 互联同步GPIO   |

| 3  |                 |     | 1.8V   |            |

| 4  | S_SYS_CLKIN_38M | 1   | LVCMOS | 互联从模组同步时钟输 |

| 4  | 4               |     | 1.8V   | 入          |

| 5  | M_SYS_CLKOUT_38 | 0   | LVCMOS | 互联主模组同步时钟输 |

| 3  | M4              |     | 1.8V   | 出          |

| 6  | S_SYS_RSTIN#    | I   | LVCMOS | 互联从模组系统复位信 |

| O  |                 |     | 1.8V   | 号输入        |

| 7  | M_SYS_RSTOUT#   | 0   | LVCMOS | 互联主模组系统复位信 |

| ,  |                 |     | 1.8V   | 号输出        |

| 8  | PMU_RSTIN#      | 1   | LVCMOS | 互联模组PMU复位信 |

| 0  |                 |     | 1.8V   | 号输入        |

| 9  | PMU_RSTOUT#     | 0   | LVCMOS | 互联模组PMU复位信 |

| 7  |                 |     | 1.8V   | 号输出        |

- 1. 该信号专用于双模组互联使用,单模组时悬空即可;

- 2. 双模组互联时不使用引脚悬空即可;

接口说明

# 8.12 配置信号

# 8.12.1 配置引脚

# AI310SM算力模组提供了必要的模式配置引脚。

| 序号 | 信号名称              | 方向 | IO电平        | 描述                                                                                                                                     |

|----|-------------------|----|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1  | M_DUAL_SEL#       | I  | LVCMOS 1.8V | 单模组双模组模式配置 1: 单模组 0: 双模组 模组内部上拉到1.8V,默认为单模组模式 悬空表示选择为单模组模式, 0欧姆电阻接地表示选择为双模组模式; 单模组时必须悬空                                                |

| 2  | M_MASTER_SEL      | I  | LVCMOS 1.8V | 区分主模组/从模组<br>1:主模组<br>0:从模组<br>模组内部上拉到1.8V,默认为主模组模式<br>悬空表示选择为主模组模式,0欧姆电阻接地表示选择为从模组<br>模式;单模组时必须悬空                                     |

| 3  | M_PCIERC_SEL#     | 1  | LVCMOS 1.8V | RC/EP 模式选择  1: EP 模式 0: RC 模式 模组内部上拉到1.8V,默认为EP模式 悬空表示选择为EP模式,0欧姆电阻接地表示选择为RC模式;当配置为双模组模式时,两个模组的RC/EP必须配置为相同的模式                         |

| 4  | M_RSVD_STRAP<br>0 | I  | LVCMOS 1.8V | M_RSVD_STRAP[4,1:0] 系统引导方式选择,仅在RC模式时需要配置                                                                                               |

|    | M_RSVD_STRAP<br>1 | I  | LVCMOS 1.8V | 000 核心板eMMC<br>001 PXE FTP                                                                                                             |

| 5  | M_RSVD_STRAP<br>4 | I  | LVCMOS 1.8V | 010 PXE HTTPS<br>011 USB盒<br>100 SATA HDD<br>101 PCIE M.2硬盘<br>110 CD (虚拟光驱)<br>111 TBD<br>模组内部上拉到1.8V,默认为TBD<br>配置时只需将相应引脚进行0欧姆电阻接地即可 |

| 6  | M_HKADC_IN0       | I  | LVCMOS 1.8V | M_HKADC_IN[2:0] BOARD ID配置                                                                                                             |

| 7  |                   |    | LVCMOS 1.8V | 模组内部通过20K电阻上拉到1.8V                                                                                                                     |

| 8  | M_HKADC_IN2       |    | LVCMOS 1.8V | 配置时只需将相应引脚进行相应阻值电阻接地即可<br>EP模式时必须配置为201;<br>RC模式根据具体应用需求进行配置;                                                                          |

# 8.12.2 BOARD ID配置

M\_HKADC\_IN[2:0]详细取值定义如下表推荐分压电阻阻值所示,其中AI310SM算力模组内部M\_HKADC\_IN[2:0]通过20K电阻上拉至1.8V,用户可通过载板不同取值的下拉电阻确定M\_HKADC\_IN[2:0]的取值。

Board\_ID 配置示例图

| 取值 | 上拉电阻R1(Kohm) | 下拉电阻R2(Kohm) |

|----|--------------|--------------|

| 0  | 20           | 0            |

| 1  |              | 2            |

| 2  |              | 5.6          |

| 3  |              | 10           |

| 4  |              | 15           |

| 5  |              | 27           |

| 6  |              | 47           |

| 7  |              | 68           |

| 8  |              | 200          |

| 9  |              | NC           |

接口说明

# 不同Board ID对应应用场景如下表所示

|      | EP                                                                                                    |                                               |                                                 |  |  |  |  |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 端口名  | M PCIE TX/RX[7:0]                                                                                     | M PCIE TX/RX[11:8]                            | M PCIE TX/RX[15:9]                              |  |  |  |  |  |  |  |  |  |

| 规格   | х8                                                                                                    | x4                                            | x4                                              |  |  |  |  |  |  |  |  |  |

| LINE | PCIe lane0   PCIe lane1   PCIe lane2   PCIe lane3   PCIe lane4   PCIe lane5   PCIe lane6   PCIe lane7 | PCIe lane8 PCIe lane9 PCIe lane10 PCIe lane11 | PCIe lane12 PCIe lane13 PCIe lane14 PCIe lane15 |  |  |  |  |  |  |  |  |  |

| 201  |                                                                                                       | PCIEX16                                       |                                                 |  |  |  |  |  |  |  |  |  |

|    | 端口名                                   | 规格               | LINE            | 201           | 202    | 203         | 204          | 205    | 206    | 207    | 208           | 209          | 210    | 211    | 212    | 213    | 214    | 215    | 216    |       |       |

|----|---------------------------------------|------------------|-----------------|---------------|--------|-------------|--------------|--------|--------|--------|---------------|--------------|--------|--------|--------|--------|--------|--------|--------|-------|-------|

|    |                                       |                  | PCIe lane0      |               |        |             |              | PCIEX2 | PCIEX2 |        |               |              | PCIEX2 | PCIEX2 |        |        |        | PCIEX2 | PCIEX2 |       |       |

|    |                                       |                  | PCIe lane1      | 2             |        |             | EIEX4 PCIEX4 | TOTEAL | TCILAL |        |               |              | TOTLAG | TOTERS | 1      |        |        | TCILAL | TOTERS |       |       |

|    |                                       |                  | PCIe lane2      |               |        | PCIEX4      |              | PCIEX2 | PCIEX2 |        | PCIEX4        | CIEX4 PCIEX4 | PCIEX2 | PCIEX2 |        | PCIEX4 | PCIEX4 | PCIEX2 | PCIEX2 |       |       |

|    |                                       |                  | PCIe lane3      |               |        |             |              |        |        |        |               |              |        |        |        |        |        |        |        |       |       |

|    | M_PCIE_TX/RX[7:0]                     | x8               | PCIe lane4      |               | PCIEX8 |             | PCIEX2       |        | PCIEX2 | PCIEX8 |               | PCIEX2       |        | PCIEX2 | PCIEX8 |        | PCIEX2 |        | PCIEX2 |       |       |

|    | (PCIE)                                |                  | PCIe lane5      |               |        |             |              |        |        |        |               |              |        |        |        |        |        |        |        |       |       |

|    |                                       |                  | PCIe lane6      |               |        | PCIEX4      | PCIEX2       | PCIEX4 | PCIEX2 |        | PCIEX4 PCIEX2 | PCIEX4       | PCIEX2 |        | PCIEX4 | PCIEX2 | PCIEX4 | PCIEX2 |        |       |       |

| RC |                                       |                  | PCIe lane7      | PCIEX16       |        |             |              |        |        |        |               |              |        |        |        |        |        |        |        |       |       |

|    |                                       |                  | PCIe lane8      |               |        |             |              |        | XGEO   | XGEO   | XGEO          | XGEO         | XGE0   | XGE0   | XGEO   | XGEO   | XGEO   | XGEO   |        |       |       |

|    | M_PCIE_TX/RX[11:8] x4                 | x4               | PCIe lane9      |               |        |             |              |        |        | XGE1   | XGE1          | XGE1         | XGE1   | XGE1   | XGE1   | XGE1   | XGE1   | XGE1   | XGE1   |       |       |

|    | (PCIE;XGE)                            |                  | PCIe lane10     |               |        |             |              |        |        | XGE2   | XGE2          | XGE2         | XGE2   | XGE2   | XGE2   | XGE2   | XGE2   | XGE2   | XGE2   |       |       |

|    |                                       |                  | PCIe lane11     |               |        |             |              |        |        | XGE3   | XGE3          | XGE3         | XGE3   | XGE3   | XGE3   | XGE3   | XGE3   | XGE3   | XGE3   |       |       |

|    | M_PCIE_TX/RX[15:9]<br>(PCIE,XGE;SATA) |                  | PCIe lane12     |               | PCIEX8 | PCIEX8      | PCIEX8       | PCIEX8 | PCIEX8 | XGE4   | XGE4          | XGE4         | XGE4   | XGE4   | SATAO  | SATA0  | SATAO  | SATAO  | SATAO  |       |       |

|    |                                       |                  | PCIe lane13     |               |        |             |              | 7,000  |        | XGE5   | XGE5          | XGE5         | XGE5   | XGE5   | SATA1  | SATA1  | SATA1  | SATA1  | SATA1  |       |       |

|    |                                       | x4               | PCIe lane14     |               |        |             |              |        |        | XGE6   | XGE6          | XGE6         | XGE6   | XGE6   | SATAZ  | SATA2  | SATA2  | SATA2  | SATA2  |       |       |

|    |                                       | (I CILACE, SAIA) | (LOLLAGE, SATA) | (I CILANDAIA) |        | PCIe lane15 |              |        |        |        |               |              | XGE7   | XGE7   | XGE7   | XGE7   | XGE7   | SATA3  | SATA3  | SATA3 | SATA3 |

- 1. 建议所有配置信号预留下拉电阻;

- 2. 目前RC模式华为未正式开放具体应用配置,以上配置仅供参考;

# 8.13 IPMC信号

## AI310SM算力模组板载BMC功能,可以进行模组健

康状态监控、风机控制、上下电控制等功能。

| 序号 | 信号名称          | 方向  | IO电平        | 描述                   |

|----|---------------|-----|-------------|----------------------|

| 1  | IPMC_I2C2_SCL | 1/0 | LVCMOS 3.3V | BMC I2C时钟,模组内部已有4.7K |

| I  |               |     |             | 电阻上拉到3.3V            |

|    | IPMC_I2C2_SDA | 1/0 | LVCMOS 3.3V | BMC I2C数据,模组内部已有4.7K |

| 2  |               |     |             | 电阻上拉到3.3V            |

| 7  | IPMC_UARTD_RX | 1/0 | LVCMOS 3.3V | BMC调试串口的接收数据线,模组     |

| 3  |               |     |             | 内有上拉电阻               |

| 4  | IPMC_UARTD_TX | I   | LVCMOS 3.3V | BMC调试串口的发送数据线        |

| 5  | IPMC_PWM      | 0   | LVCMOS 3.3V | BMC风机PWM控制信号         |

#### 注意:

- 1. 不使用时, 引脚直接悬空;

- 2. 调试串口波特率115200bps, 8位数据为, 1位停止位, 无奇偶校验位;

- 3. I2C协议待后续更新;

### 8.14 其他信号

| 序号 | 信号名称      | 方向 | IO电平        | 描述                                                                                    |

|----|-----------|----|-------------|---------------------------------------------------------------------------------------|

| 1  | PWR_BT#   | I  | LVCMOS 3.3V | 外部开关机输入信号,模组内部已有上拉,低电平有效,<br>短按(≤1s)开机,长按(≥5s)关机;可连接到开关机<br>按键;<br>RC模式下可用,EP模式拉高或悬空; |

| 2  | BT_RST#   | I  | LVCMOS 3.3V | 外部复位输入信号,模组内部已有上拉,低电平有效,可<br>连接到复位按键;<br>RC模式下可用,EP模式拉高或悬空;                           |

| 3  | M_OS_EXIT | 0  | LVCMOS 3.3V | 系统退出标志,RC模式可用,为预留功能                                                                   |

注意: 不使用时, 引脚直接悬空;

接口说明

# 8.15 电源输入

# AI310SM算力模组采用DC 12V进行供电。

| 序号 | 信号名称     | 方向 | 电平  | 描述                            |

|----|----------|----|-----|-------------------------------|

| 1  | P12V     | I  | 12V | +12V电源输入,12V±5%,电流≥8A,纹波≤50mV |

|    |          |    |     | +3V RTC电源输入,+2.7V~+3.3V       |

| 2  | P3V3_BAT | I  | 3V  | 仅在RC模式下RTC功能可用,必须提供此电源;       |

|    |          |    |     | EP模式下该引脚可直接悬空;                |